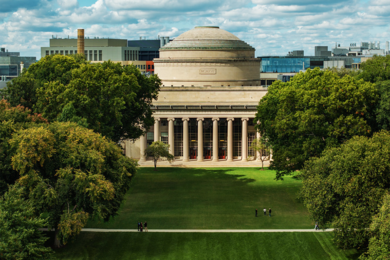

The Singapore-MIT Alliance for Research and Technology (SMART) has entered its eighth year of investigating new technologies that could serve Singapore and other future-looking cities. At the same time, this collaboration between MIT and the National Research Foundation of Singapore (NRF) is exploring new concepts in the process of research and development itself. SMART is not only better funded than most R&D projects; it’s also distinct in its interdisciplinary and iterative approach to innovation.

MIT may push interdisciplinary collaboration more than most universities, but SMART takes the concept to a whole new level. “SMART uses a different model than anything in the U.S.,” says Eugene A. Fitzgerald, the Merton C. Flemings-SMA Professor of Materials Science and Engineering at MIT, who heads up the SMART Low Energy Electronic Systems (LEES) group. “We bring together faculty with expertise in different areas to collaborate closely from start to finish. In larger, multi-investigator programs, we typically simulate that sort of interdisciplinary approach, but we end up dividing the programs into different disciplines.”

The SMART LEES research program is marked by an iterative process of discovery in which researchers periodically reconsider the potential applications of an emerging technology. This involves evaluating how the latest changes to an emerging design, as well as new technological, economic, and social trends, might affect its purpose or its manufacturing and distribution.

The iterative process dovetails nicely with SMART’s interdisciplinary approach. As a former SMA Fellow in the Singapore-MIT Alliance (SMA) from 1999-2009, Fitzgerald has seen this in action. “A circuit designer might imagine a particular kind of circuit, which then motivates materials and device people to build prototypes, which then induce new ideas in the designer,” he says. “The idea is to create a new white space of innovation that industry would not converge upon naturally.”

SMART will soon begin evaluating what new and existing programs will be funded in the third five-year term starting in 2017. SMART programs are chosen through a competitive process at MIT, with further review of finalists by Singapore’s NRF.

Some programs may take only five or 10 years while others could extend to a 15-year period. “True fundamental innovation takes 10 to 15 years to reach market, so giving these projects enough time is important,” says Fitzgerald. “In the U.S., programs like this tend to last only three years, at which point valuable innovations can be terminated or interuppted.”

SMART’S labs at NRF’s Campus for Research Excellence and Technological Enterprise (CREATE) represent the first major MIT facility outside of Massachusetts. Approximately 50 MIT faculty members are involved in SMART, more or less equally split between LEES and four other programs: BioSystems and Micromechanics (BioSyM); the Center for Environmental Sensing and Modeling (CENSAM); Future Urban Mobility (FM); and Infectious Diseases (ID). There is always at least one resident MIT professor per program working at the SMART labs at CREATE, and all 50 SMART faculty members spend one month a year in Singapore.

The interchange benefits MIT as much as Singapore, says Fitzgerald. “SMART offers MIT faculty an opportunity to work with considerable resources and an interesting new research model.”

The current projects follow Singapore’s goal of creating a “smart nation” with a knowledge-based economy that enables a higher GDP per person, says Fitzgerald. While projects are developed with Singapore’s future in mind, they all have broader applicability. Projects tackle global challenges such as the need to more effectively communicate knowledge, improve efficiency, and increase mobility in the city of the future, he adds.

SMART has already developed several interesting new technologies, sometimes in collaboration with other institutes, such as the National University of Singapore (NUS), Nanyang Technological University (NTU), and various programs at MIT. The BioSyM group recently developed a technique for detecting malaria within minutes; the ID group recently joined with a multinational research team including Duke University, NUS, NTU, and MIT to announce the development of a viable dengue therapeutic for all dengue serotypes; CENSAM built a multifunction “LEDIF” sensor device for analyzing water quality, which is being deployed on a NUS autonomous underwater vehicle; the FM group worked with NUS to launch the first driverless cars authorized for use on Singapore’s streets; and LEES is combining new integrated circuit technology with existing fabrication methods.

SMART LEES: Optical chips from III-V and silicon

At the four-year old SMART LEES program, Fitzgerald is leading a team working on incorporating new materials into semiconductor systems. An early focus is on lattice-mismatched materials, the process of integrating layers in electronic materials and devices with different lattice parameters. Holding true to SMART’s interdisciplinary charter, LEES draws on faculty and students from material sciences, devices, processing, and circuit design.

Fitzgerald was one of the key developers of silicon-germanium lattice mismatch strain engineering at Bell Labs in the early '90s, and he continued his research into the new millennium at MIT, where he helped spin off AmberWave to commercialize strained silicon. Now, he is leading SMART LEES in experimenting with new monolithic, lattice-mismatched integrated circuits using III-V (3-5) semiconductor materials combined with silicon complimentary metal oxide semiconductor (CMOS) technology.

“We’re looking at III-V materials that have great optical properties and are better at power management and communication than silicon,” Fitzgerald says.

Until recently, the integration of III-V semiconductors with silicon has been stymied by the fact that the sizes of the lattice constant are fundamentally different, thereby producing a high level of defects. In recent years, Fitzgerald has modified the process he used to control defect densities in strained silicon for III-V semiconductors. Each principal investigator in the SMART LEES program can contribute his or her expertise to the goal of creating new circuits incorporating new materials, resulting in new functionality in electronic circuits.

Today’s processor cores communicate using silicon circuits, which consume a great deal of power. “A III-V device with optimized lattice matching and a very small footprint could span the tiny currents inside the core all the way to higher on-chip voltages needed for communication,” Fitzgerald says. The technology could reduce cellphone power consumption by offloading communication and sync, he adds.

“With integrating III-V and other materials with silicon technology, we are designing circuits that nobody could conceive of, such as building lighting systems on a chip,” Fitzgerald explains. “We’re making the silicon fab the entire supply chain for the lighting system, so you get a complete programmable lighting surface, including driver circuitry and intelligence in a very small footprint. Ideally, you could drop a III-V devices into circuits whenever you want to communicate with the outside world, by wireless or optical communication.”

The monolithic integration of LEDs with silicon electronics could greatly reduce the cost of smart LED lighting, and potentially lead to thin displays with their own optical inter-device communications via light pulses. The result might be a more secure alternative to WiFi, he adds.

“Once the display and computer merge into a single device, you can define new capabilities,” says Fitzgerald. “For example, a very thin display with multiple functionality in a single device is possible. This opens up possibilities such as a smartwatch display that is also a solar cell that charges the device. You could even reprogram the same display to act as a scanner.”

Initially, the technology will be used for a variety of task-specific devices with similar hardware. “But once volume ramps up you could have common platforms where all these capabilities reside,” Fitzgerald says. “It would be like a tricorder where you can program it to do a lot of different things.”

SMART LEES is also experimenting with a business model that makes it easier for novel integrated circuits to reach market. “Today we have huge fabs that ship huge amounts of wafers,” Fitzgerald says. “The problem is that whenever someone comes up with a new device or material, it’s difficult to insert it into the manufacturing infrastructure. They’re making sugar cookies and you’re telling them you want chocolate chip cookies — and they don’t want chocolate chips anywhere near their facilities.”

The SMART LEES solution is to use a standard design kit to build upon a standard wafer made in a real fab, but then stop the manufacturing process in the middle. “At that point, we bring the wafer back to R&D to add new materials or devices in a way that can be compatible with the fab,” Fitzgerald explains. “The device can then be finished using the standard processes. This way, you can produce new ICs for smaller markets without having to build a new process or a $5 billion plant for every new product.”

The combination of the integrating new materials and devices with silicon, combined with new approaches to fabrication, could lead to the same sort of long-lasting benefits as Moore’s Law, says Fitzgerald. He notes, however, that “the next paradigm usually comes from where you least expect it.”